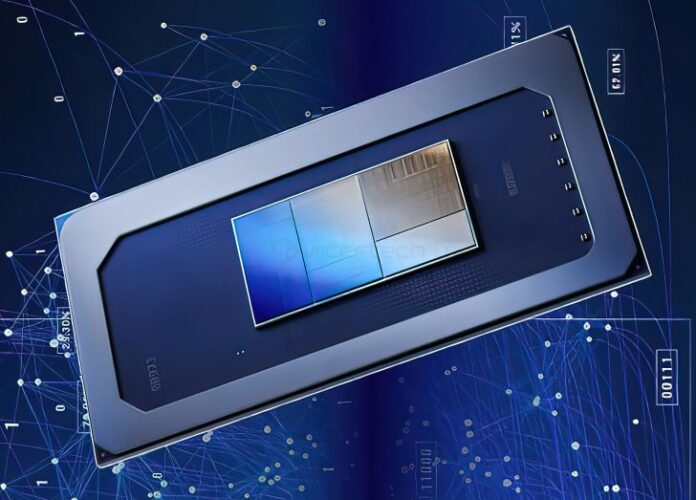

Intel's Meteor Lake CPU lineup is set to be a significant breakthrough for the company and we have some insights from ASCII who estimate just how many chips CPU tiles can be secured each month to supply to end-users.

Intel's Next-Gen Meteor Lake CPU Tiles In Production For Future Client PC Platforms

In a Q&A session with Intel officials, it was revealed that the "Intel 4" manufacturing process has seen obstacles with mass manufacturing, with limited facilities having the capability to fabricate the process. It was disclosed that "Intel 4" is in mass production at the D1 division Oregon facility, with total output reaching 40,000 monthly wafers. While the company has expressed confidence in its "Intel 4" process node, they also plan to set up other facilities as well since there is still uncertainty surrounding the supply.

The folks at ASCII got to see a close-up of the Intel Meteor Lake CPU tile wafer. The size of the entire Meteor Lake tile (base tile) is estimated to be 23.1mm x 11.5mm. The CPU tile is reportedly around 8.9 x 8.3 mm or 73.9 mm2 (estimation not final), which leads to the conclusion that approximately 730 tiles in total can be obtained by a single wafer.

Moving to the crux, if we estimate a 50% yield rate of Intel 4 (which isn't confirmed yet), that leads to 365 CPU chips through a single wafer. If Intel reaches 1000 unit wafer output per month, that leads to 365,000 CPU tiles. One shouldn't worry about other tiles such as GPU, since those are based on TSMC's N5 and N6 processes, both of which have reached to a proficient level.

As for whether this is a good figure or not, it is stated that it should be sufficient for the laptop masses but not optimal for desktop chips which may explain why the CPUs got canned in the first place. That said, Intel's 6+8 Desktop CPUs were rumored to be using a repurposed Meteor Lake-P die. Intel is expected to unveil some more details of Meteor Lake CPUs at Hot Chips today followed by an official introduction next month at the Innovation event. The actual launch is said to take place this fall.

Intel Mobility CPU Lineup:

| CPU Family | Lunar Lake | Arrow Lake | Meteor Lake | Raptor Lake | Alder Lake |

|---|---|---|---|---|---|

| Process Node (CPU Tile) | Intel 18A? | Intel 20A '5nm EUV" | Intel 4 '7nm EUV' | Intel 7 '10nm ESF' | Intel 7 '10nm ESF' |

| Process Node (GPU Tile) | TSMC 3nm? | TSMC 3nm | TSMC 5nm | Intel 7 '10nm ESF' | Intel 7 '10nm ESF' |

| CPU Architecture | Hybrid | Hybrid (Four-Core) | Hybrid (Triple-Core) | Hybrid (Dual-Core) | Hybrid (Dual-Core) |

| P-Core Architecture | TBD | Lion Cove | Redwood Cove | Raptor Cove | Golden Cove |

| E-Core Architecture | TBD | Skymont | Crestmont | Gracemont | Gracemont |

| Top Configuration | TBD | TBD | 6+8 (H-Series) | 6+8 (H-Series) 8+16 (HX-Series) | 6+8 (H-Series) 8+8 (HX-Series) |

| Max Cores / Threads | TBD | TBD | 14/20 | 14/20 | 14/20 |

| Planned Lineup | U Series? | H/P/U Series | H/P/U Series | H/P/U Series | H/P/U Series |

| GPU Architecture | Xe2-LPG (Battlemage) | Xe-LPG (Alchemist) | Xe-LPG (Alchemist) | Iris Xe (Gen 12) | Iris Xe (Gen 12) |

| GPU Execution Units | 64 EUs | 192 EUs | 128 EUs (1024 Cores) | 96 EUs (768 Cores) | 96 EUs (768 Cores) |

| Memory Support | TBD | TBD | DDR5-5600 LPDDR5-7400 LPDDR5X - 7400+ | DDR5-5200 LPDDR5-5200 LPDDR5-6400 | DDR5-4800 LPDDR5-5200 LPDDR5X-4267 |

| Memory Capacity (Max) | TBD | TBD | 96 GB | 64 GB | 64 GB |

| Thunderbolt 4 Ports | TBD | TBD | 4 | 4 | 4 |

| WiFi Capability | TBD | TBD | WiFi 6E | WiFi 6E | WiFi 6E |

| TDP | TBD | TBD | 7W-45W | 15-55W | 15-55W |

| Launch | ~2025 | 2H 2024 | 2H 2023 | 1H 2023 | 1H 2022 |

WccftechContinue reading/original-link]