A super-early Intel Lunar Lake CPU has been spotted within the SiSoftware database which packs 20 cores and up to 3.9 GHz boost clocks.

Intel Lunar Lake CPUs Are Up & Running: 20 Core Engineering Sample Spotted With Up To 3.91 GHz Clocks

At Innovation 2023, Intel showcased the very first demo of an early Lunar Lake CPU which booted into the operating system and was running an AI workload, showcasing its stability. Now, the same Lunar Lake CPUs are showing up in online databases with one early sample making its way to the SiSoftware database.

The Intel Lunar Lake CPU sample was recently added to the database (3rd October 2023) so it may as well be the same chip that we saw during the event. As for specifications, the Lunar Lake ES chip comes packed with 20 cores which operate at a base frequency of 1.0 GHz and a boost frequency of 3.91 GHz for the P-Core and 2.61 GHz for the E-Core cluster.

It was recently reported that Lunar Lake CPUs will retain the Lion Cove P-Core and Skymont E-Core architecture which is the same that is used for Arrow Lake chips. It is also likely that the compute tile will be based on the 20A process.

The chip features 10 MB of L2 cache for the P-Core clusters and 4 MB of L2 cache for the E-Core clusters for a combined total of 14 MB L2 cache. The entire chip features a shared 16 MB L3 cache too. That's 25% higher L2 cache for the P-Cores versus the upcoming Redwood Cove cores which are equipped with 2 MB L2 cache per core. But at the moment it is too early to tell what the final core/thread count of this chip would be and how they will be split between the P-Cores & E-Cores.

The Intel Lunar Lake CPU was running at an average power of 17W since the lineup is focusing on the mobility segment with improved performance/watt gains. The CPU itself was running on Intel's Reference Evaluation Platform with LPDDR5 memory and is marked as a LNL-M chip. The chip was tested in the Processor Cryptography (High Security) workload and despite its super early nature, it managed to come out on par with Intel's top Tiger Lake chip, the i7-1195G7, with similar bandwidth results.

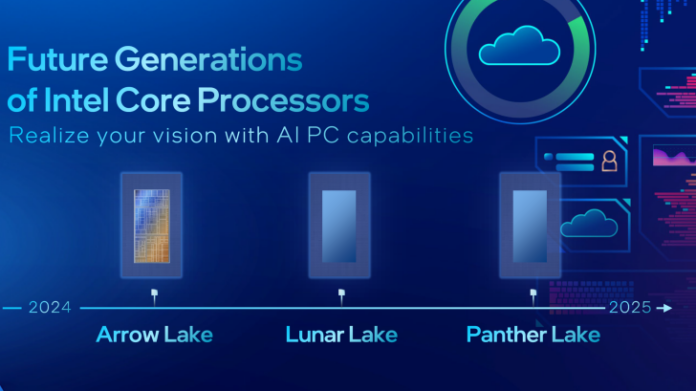

Intel's Lunar Lake CPUs are targeting production in the second half of 2024 followed by a launch in 2025. The chips will be replacing Arrow Lake as the next-gen mobility family and we can expect a few big upgrades, especially in the graphics department which will be upgraded to the next-gen Xe2 or Battlemage architecture.

Intel Mobility CPU Lineup:

| CPU Family | Lunar Lake | Arrow Lake | Meteor Lake | Raptor Lake | Alder Lake |

|---|---|---|---|---|---|

| Process Node (CPU Tile) | Intel 20A? | Intel 20A '5nm EUV" | Intel 4 '7nm EUV' | Intel 7 '10nm ESF' | Intel 7 '10nm ESF' |

| Process Node (GPU Tile) | TSMC 3nm? | TSMC 3nm | TSMC 5nm | Intel 7 '10nm ESF' | Intel 7 '10nm ESF' |

| CPU Architecture | Hybrid | Hybrid (Four-Core) | Hybrid (Triple-Core) | Hybrid (Dual-Core) | Hybrid (Dual-Core) |

| P-Core Architecture | Lion Cove? | Lion Cove | Redwood Cove | Raptor Cove | Golden Cove |

| E-Core Architecture | Skymont? | Skymont | Crestmont | Gracemont | Gracemont |

| LP E-Core Architecture (SOC) | Skymont? | Crestmont? | Crestmont? | N/A | N/A |

| Top Configuration | TBD | TBD | 6+8 (H-Series) | 6+8 (H-Series) 8+16 (HX-Series) | 6+8 (H-Series) 8+8 (HX-Series) |

| Max Cores / Threads | TBD | TBD | 14/20 | 14/20 | 14/20 |

| Planned Lineup | U Series? | H/P/U Series | H/P/U Series | H/P/U Series | H/P/U Series |

| GPU Architecture | Xe2-LPG (Battlemage) | Xe-LPG (Alchemist) | Xe-LPG (Alchemist) | Iris Xe (Gen 12) | Iris Xe (Gen 12) |

| GPU Execution Units | 64 EUs | 192 EUs | 128 EUs (1024 Cores) | 96 EUs (768 Cores) | 96 EUs (768 Cores) |

| Memory Support | TBD | TBD | DDR5-5600 LPDDR5-7400 LPDDR5X - 7400+ | DDR5-5200 LPDDR5-5200 LPDDR5-6400 | DDR5-4800 LPDDR5-5200 LPDDR5X-4267 |

| Memory Capacity (Max) | TBD | TBD | 96 GB | 64 GB | 64 GB |

| Thunderbolt 4 Ports | TBD | TBD | 4 | 4 | 4 |

| WiFi Capability | TBD | TBD | WiFi 6E | WiFi 6E | WiFi 6E |

| TDP | TBD | TBD | 7W-45W | 15-55W | 15-55W |

| Launch | ~2025 | 2H 2024 | 2H 2023 | 1H 2023 | 1H 2022 |

WccftechContinue reading/original-link]